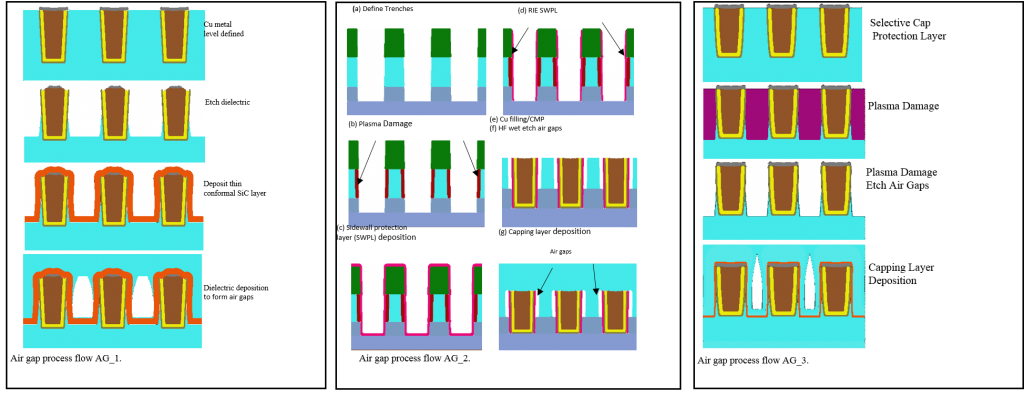

In the metallization step, a structure undergoes a diffusion barrier etch step. The copper dual damascene process involves three main parts: metallization low-k dielectrics and the capping layer. For this, chipmakers use 193nm immersion and multiple patterning. Initially, in the flow, each level of a given chip structure must be patterned to create the wiring schemes. In the BEOL, there are many process steps, which fall into two categories - patterning and the dual damascene process. Interconnects, the tiny wiring schemes in devices, are becoming more compact at each node, causing a resistance-capacitance (RC) delay in chips. The backend-of-the-line (BEOL) is second major stage of the semiconductor manufacturing process where the interconnects are formed within a device.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. Archives

December 2022

Categories |

RSS Feed

RSS Feed